台積電(TSMC)的目標是2025年量產其N2工藝,而現階段主要是其他N3工藝的產量和良品率,這被認為是世界上最先進的晶片製造技術之一。隨著英特爾Meteor Lake延期,以及N3工藝的效能未讓蘋果滿意,台積電很可能放棄N3工藝,將重點轉移到明年量產的N3E工藝,這屬於第二版3nm製程。

雖然台積電短期內的工藝推進計劃似乎受到了一些挫折,不過並沒有影響其技術的研發,近期台積電負責研發和技術的高級副總裁YJ Mii博士分享了更多的信息。據Wccftech報導,台積電下一階段將轉向具有更大鏡頭的機器,計劃在2024年引入High-NA EUV光刻機,一般認為會用於2nm晶片的製造上。

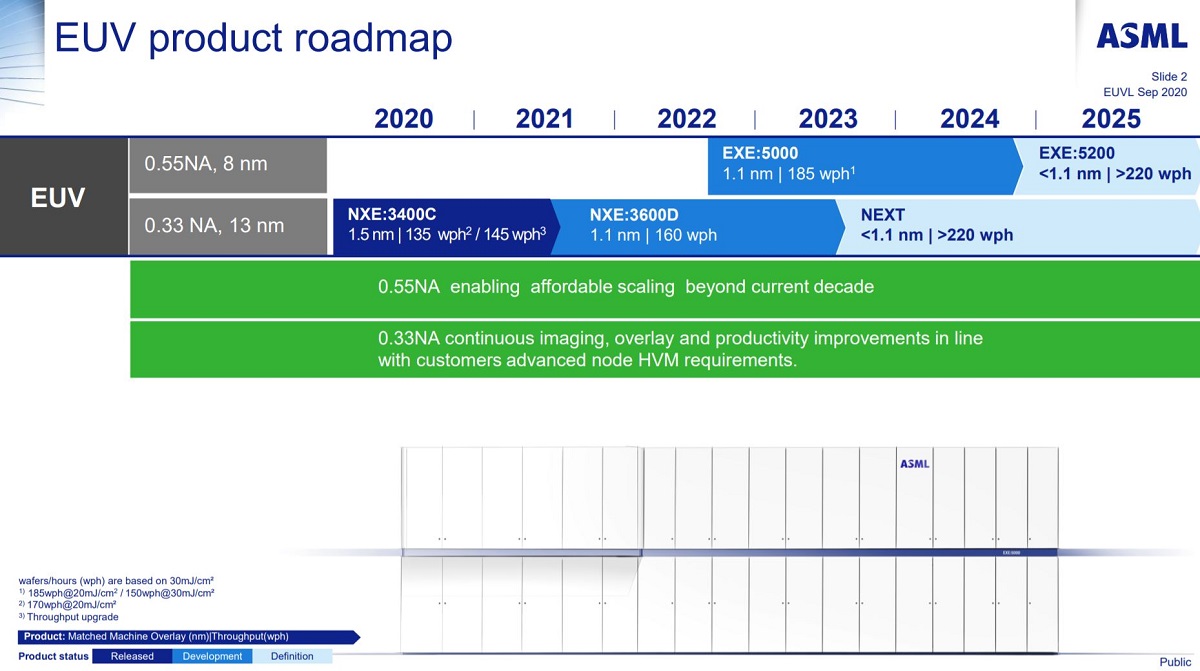

據ASML(阿斯麥)的介紹,具有高數值孔徑(High-NA)的新型EUV系統將提供0.55數值孔徑,與此前配備0.33數值孔徑透鏡的EUV系統相比,精度會有所提高,可以實現更高解析度的圖案化,以實現更小的電晶體特徵,同時每小時能生產超過200片晶圓。此前英特爾已宣布購買業界首個TWINSCAN EXE:5200系統,計劃從2025年使用High-NA EUV進行生產。

台積電在2024年拿到High-NA EUV光刻機後,初期僅用於研發和協作,期間會按照自己的要求進行調整,適當時候再用於大規模生產。與3nm製程節點不同,2nm製程節點將使用Gate-all-around FETs(GAAFET)電晶體,台積電稱相比3nm工藝會有10%到15%的性能提升,還可以將功耗降低25%到30%。預計N2工藝於2024年末將做好風險生產的准備,並在2025年末進入大批量生產,客戶在2026年就能收到首批晶片。

來源:超能網