關於蘋果的自研晶片 M1 系列仍然有著許多謎題。

也就在最近,關於 M1 晶片的後續,M2、M3 的傳聞紛沓至來,不過多是一些捕風捉影的信息,對於架構、性能、核心這些都沒有特別明確的信息,而更多的是圍繞台積電工藝節點的升級。

▲ M1 還沒出完,M2、M3 或許就要來了. 圖片來自:progamer

台積電 4nm、3nm 等新的製程工藝可能會是較大的升級點。如此來說,在能耗比上已驚艷眾人的 M1 系列,M2、M3 只增不減。

只是,在兩年後,當節點工藝升級到 3nm 之後呢?

大概有兩條,一條是把節點工藝干到 1nm,無線逼近物理極限,但難上加難。另一條是繞過節點工藝升級帶來的福利,走 Chiplet「小晶片」之路。

一顆 M1 Max 不夠?那就給 Mac Pro 裝上兩顆

不過,一向不喜歡被供應鏈擺布的蘋果,在吃節點、ARM 晶片高能效比優勢的同時,或許也在找可行之法。

從 M1 到性能更強的 M1 Pro、M1 Max,它們有著幾乎相同的架構,單核心的性能釋放較為接近,最大的不同其實是在核心數目上。

甚至,你也可以簡單的理解為,基於 ARM 的 M 晶片是靠著堆核心數目來獲得更高的性能天花板。

- M1:CPU 4+4 核,GPU 8 核,160 億電晶體,16 核心神經網絡;

- M1 Pro:CPU 2+8 核,GPU 16 核,337 億電晶體,16 核心神經網絡;

- M1 Max:CPU 2+8 核,GPU 32 核;570 億電晶體,16 核心神經網絡;

而簡單的從另一個維度來看,M1 晶片面積約 120mm²,M1 Pro 為 245mm²,到了 M1 Max 這里就直接飆升到 M1 Max 432mm²。

同一代 M 晶片,越 Max,核心數、晶片面積也就越 Max,從這里也不難理解蘋果對 M 晶片的命名規則了,通俗易懂,微軟、Intel、高通真的該好好學學。

雖然蘋果晶片架構師、副總裁蒂姆・米勒特(Tim Millet)早在 11 月份就在 Upgrade 播客里詳細的闡述了蘋果研發 M 晶片的辛路歷程,但對於 M 晶片接下來如何發展,以及在 Max 基礎之上如何更 Max 隻字未提。

▲ 蘋果晶片架構師、副總裁蒂姆・米勒特(Tim Millet). 圖片來自:Apple

隨著 MacBook Pro 14/16 陸續上市,經過許多民間 DIYer 的探究,似乎也發現了蘋果讓 M1 Max 更 Max 伏筆。

那就是「放兩個 M1 Max 進去,甚至還可以加倍」。

▲ M1 Max 隱藏區域. 圖片來自:HothardWare

這個猜想實則是基於拆解後,發現 M1 Max 相對於 M1 Pro 多出了一塊「不明區域」,腦洞一番之後,猜測是為連接兩顆甚至多顆 M1 Max 預留的「高速總線」。

▲ Tim Cook:Intel,this is for you. 圖片來自:Max Tech

這也契合了此前新 iMac Pro、Mac Pro 會採用多顆 M1 Max 組成的超大顆處理器的傳聞。「這簡直就像是在玩樂高、堆積木,簡直亂拳打死老師傅」。

不過,「堆積木」這個說法並不太準確,「拼圖」更精準一些。如此來說,雙份 M1 Max 的晶片面積會相當可觀,四倍那就更前無古人了。

M1 Max Duo 超過英偉達的頂級 GPU GA100 晶片面積(826mm²)幾乎板上釘釘。

如此巨大的 SoC,縱觀整個半導體歷史,絕對能夠算上「霸王龍」級別的晶片,更別說它會基於 5nm 工藝,成本也極有可能超過任何一枚當代的晶片。

當 M 系晶片走進「侏羅紀公園」

從重達 30 噸,占地 170 平方米的初代計算機 ENIAC,到現在的桌上 PC,設備幾乎都朝著小型化、集成化發展。

而半導體世界的處理器也是如此,當工藝節點還屬於 μm 時,英特爾初代奔騰(Pentium)面積大概是 294mm²,基於 0.8μm 工藝。

▲ Intel Pentium III Xeon.

在 x86 處理器時代,Intel Pentium III Xeon 面積達到 385mm²,基於 0.18μm 工藝。但在當時,眾處理器廠商在嚴控體積打壓成本推出較為平價的 PC 以推向大眾。

後續,無論是 64 位的普及,還是工藝節點的躍升,處理器的尺寸多是控制在 500mm² 以下,成本控制,高效利用晶圓的前提下,幾近遏制住了消費級處理器面向「恐龍化」的發展。

消費半導體行業似乎也逐步從侏羅紀慢慢走向了新時代。

▲ 民間大神也在為蘋果 M 晶片的發展之路出謀劃策. 圖片來自:Twitter

而此時蘋果 M 晶片可能的發展路線似乎又繞回到了「侏羅紀」,只不過處理器尺寸躍進的同時,電晶體的密度也沒有落下。

雖然聽起來將兩枚晶片拼在一起應該不難,也無需重新設計架構、核心。但實際之中,隨著晶片面積的增加(尤其是成倍的增長),以及保證足夠良率和產能的情況下,成本直接起飛。

而蘋果的 M 系晶片依然是個消費級產品,一年前擺脫 Intel,一方面是為了控制產品力,另一方面其實還是控製成本,達到利潤最大化。大面積 SoC 飄忽不定的成本顯然不是蘋果所期望的。

▲ M1 Max 最高的統一記憶體是 64GB,那 M1 Max Duo 直接來到 128GB?

另一方面,兩枚或者更多的 M1 Max 拼接,統一記憶體(UMA)的設計也會是一個巨大的難題,重新規劃多核心的位置,引入更大的帶寬,以及更高容量的記憶體再所難免。

於公,可能是更復雜的晶片設計,於私,可能會無形增加幾倍的成本,都會是蘋果 M 晶片變得更 Max 的兩大絆腳石。

摩爾定律已成過去,日拱一卒才是當下

「集成電路上可容納的電晶體數目,約每兩年會增加一倍。」這是著名的摩爾定律,它還有另外一個說法,「每隔 18 個月,晶片的性能就會提高一倍。」

▲ MacBook Pro 16. 圖片來自:dpreview

這里的性能其實就指的是電晶體數量,M1 Max 相較於 M1 有著 3.5 倍的性能提升,恰恰也正好反應的是電晶體數量的差距。

電晶體數量翻倍在 M1 系列這里,是晶片面積增加。而從歷史來看,更多依靠的還是工藝上的進步,從 μm 到 nm 級,電晶體數量也從百萬級躍升到億級。

但是在 2013 年左右,摩爾定律就有所放緩,從彼時到現在,工藝節點的提升對於性能的收益正在不斷減少。

更先進的工藝製程,的確可以翻升電晶體數量,但也伴隨著成本和良率的變化。

▲ 台積電預計 2023 年開始投產 3nm 工藝. 圖片來自:anandtech

根據國際商業戰略公司 (IBS) 所公布的數據,設計 3nm 晶片預計將耗資 5.9 億美元,而 5nm 只要 4.16 億美元,7nm 為 2.17 億美元,28nm 不過才 4000 萬美元。

台積電此前對外宣布將會投資 200 億美元來興建 3nm 晶圓工廠,同樣是為了 3nm,三星所耗費的並不比台積電低。

而到目前為止,也只有台積電和三星在積極布局 3nm 晶圓,其他廠商並非是不想,只是花不起這錢。

另一方面,晶片的良品率隨著面積增大而降低,700mm² 的設計合格率大概只有 30%,縮小到 150mm² 良品率就飆升到 80%。

無論從哪方面來看,晶片升級之路似乎已經被堵死了。

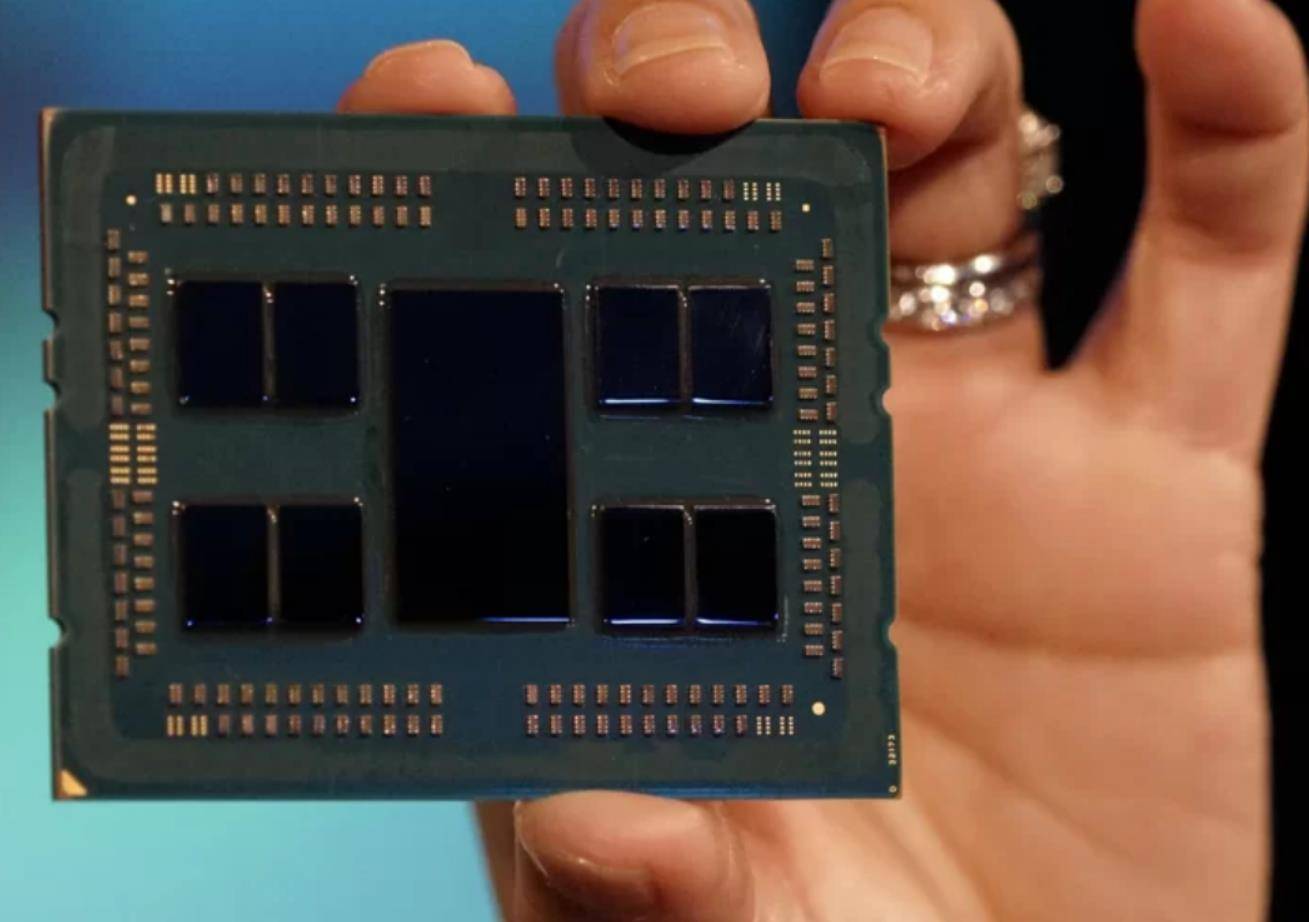

▲ AMD 基於 Zen 2 的 EPYC 2 (Rome) 處理器. 圖片來自:AMD

為了能繼續提升晶片規模和密度,不少人把目光從工藝節點的升級轉向了封裝工藝上,也就是 AMD 押寶的 Chiplet(小晶片)技術。

Chiplet 簡單來說就像湯圓餡的餃子一樣,把不同功能的小晶片封裝在一起,而不是直接從晶圓上切割,以先進的封裝工藝來彌補工藝節點的停滯。

▲ 目前對於 Chiplet 最為形象的比喻(但我不認可這種吃法).

近年來 AMD 也正是通過 Chiplet 技術不斷地提升處理器密度對 Intel 進行了逆襲,逐步開始搶奪市場。

對於近年崛起的 Chiplet,科技行業權威咨詢機構 The Linley Group 在《Why Big Chips Are Getting Small》一文中,直接提出 Chiplet 可以將大型 7nm 晶片的設計成本降低 25% 以上,而在面對 5nm 和更高工藝時,節省的成本還會更高。

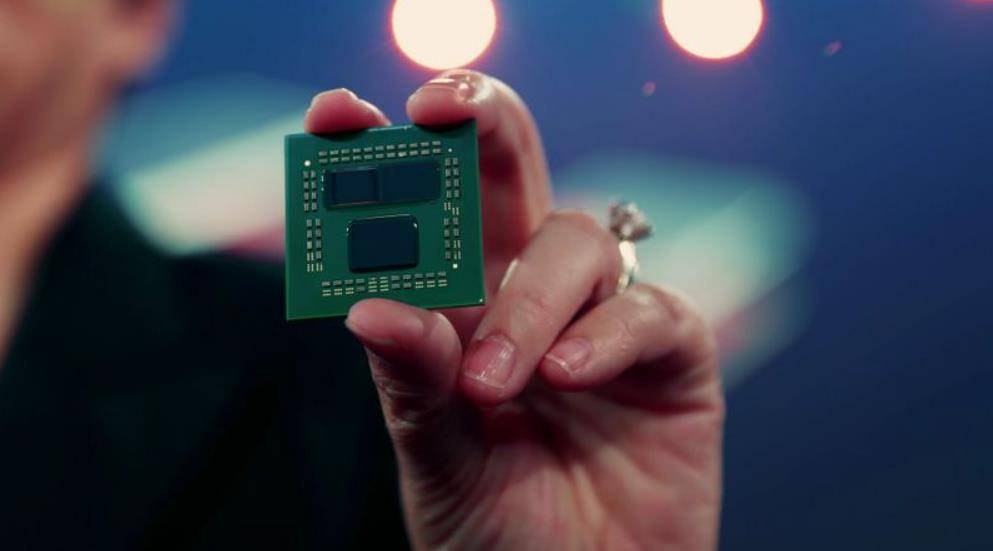

▲ AMD 基於 3D Chiplet 封裝的 Ryzen 9 5900X CPU.

而 AMD 所公布的 3D V-Cache 也在證實,舊的工藝與先進的封裝工藝所結合的 Chiplet,可以達到更高節點的性能,甚至還能把不同工藝節點的晶片進行混裝,有著足夠的靈活度。

除了降低成本,實現更先進的性能之外,Chiplet 還會加快產品面市速度,畢竟直接利用舊晶片配合先進封裝工藝即可,甚至完全可以忽略對先進工藝節點的布局。

說了這麼多好處,Chiplet 也有相應的劣勢,小晶片 2D、3D 的堆疊對熱管理設計有著相當高的要求,且封裝體內總熱功耗會有明顯的提升。

▲ 基於 Chiplet 的 Intel 伺服器晶片. 圖片來自:nextplatorm

但無論如何,Chiplet 已經被很多機構、廠商認定為後摩爾時代,在晶片上性能持續突破的重要技術。

▲ M1 inside 的 Mac mini 與 MacBook Air.

而回到最開始的蘋果自研 M 晶片上,通過 ARM 架構,以及工藝節點的升級,不斷提升能效比,順便控制下良率與成本。至於是否會通過拼接多個 M1 Max 一同組成復雜的巨型 SoC 塞入工作站級別的 Mac Pro 中,從目前來說,蘋果有足夠的的資本與實力去設計與生產出類似於「史前巨獸」的處理器。

▲ iMac Pro 2022 的非官方渲染圖.

至於 Chiplet,我想它肯定已經出現在蘋果晶片團隊中的圖紙上,與其面對未來不明朗的工藝節點提升,倒不如主動求變,憑借現行的 M 晶片、A 晶片去組合完成更深層次的 SoC 升級。

來源:愛范兒